NICのオープンソースプロジェクトCorundumを使用してAlveo U200とU50をNIC化し、Alveo間で通信ができたのでその備忘録です。

この記事のゴール

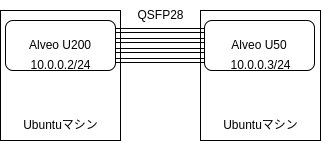

以下の画像のようにAlveo U200とAlveo U50をNIC化したもの使って通信する。

環境

基本的に前に投稿した記事Alveo U200とU50のセットアップのセットアップ環境を用いた。ただし、Vivadoは別マシンにインストールしているものを使ったためバージョンがズレている(2021.1でなく2022.1)。

- Corundum: 記事執筆時点での最新コミット(c708bc4)

- AlveoホストマシンOS: Ubuntu 20.04

- Vivado: 2022.1

- FPGA: Alveo U200/U50

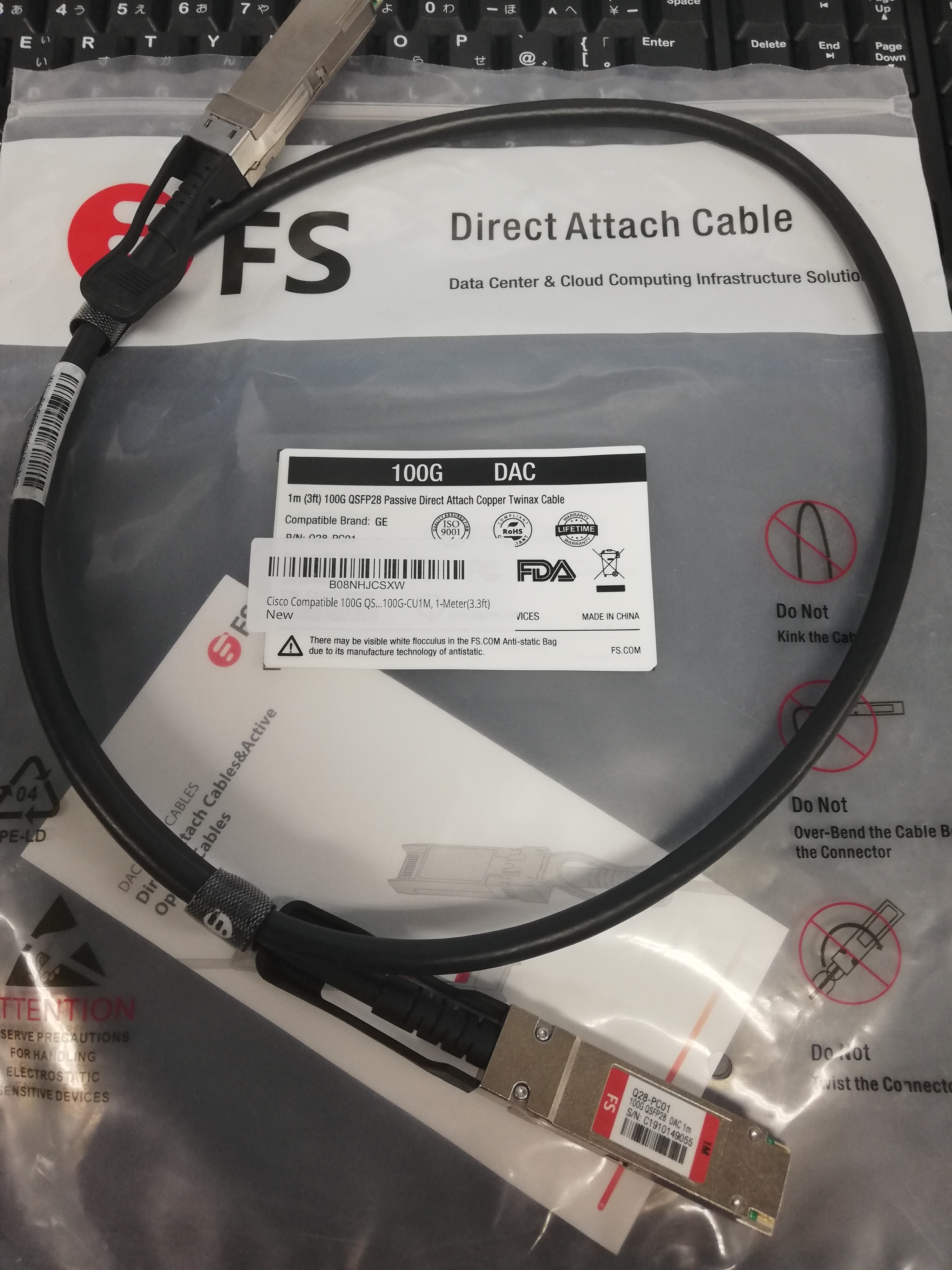

- DACケーブル: 1m (3ft) Cisco QSFP-100G-CU1M互換 100G QSFP28パッシブダイレクトアタッチ銅製Twinaxケーブル(DAC)

NIC化の手順 (U200で説明)

Corundumでは、10G/25G/100GのEthernetに対応している。今回は、U200とU50を100GbEへNIC化した。以下はCorundumのドキュメントのGetting Startedを参考に進めていったときの手順である。また、以下の説明では、U200を対象とするが、同様の手順でU50もNIC化できる。

1. UltraScale+ Integrated 100G Ethernet Subsystemのライセンス取得

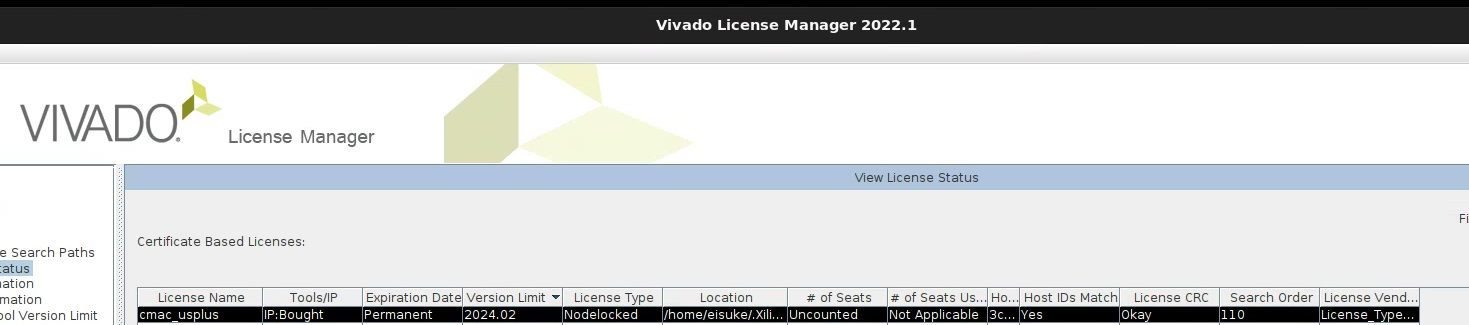

まず、XilinxのUltraScale+ Integrated 100G Ethernet Subsystemから100G Ethernet Subsystemのライセンスを取得する(無償)。また、ライセンスファイルが取得できたら、Vivadoのライセンスマネージャで読み込む。 読み込むと以下の画像のようにcmac_usplusという名前で追加された。

2. Corundumのダウンロード

GitHubからCloneする

$ git clone https://github.com/corundum/corundum.git

3. Vivadoのセットアップ

これはいつもどおりVivadoのsettings64.shを実行する。

$ source /tools/Xilinx/Vivado/2022.1/settings64.sh

4. Bitstream生成

Corundumでは、FPGAボードごとにMakefileが用意されており、makeを実行するだけでNICの回路生成まで行ってくれる。自分の環境では、1時間くらい待つと回路生成が終了した。

$ # NIC化の対象となるFPGAボードのCorundum内のディレクトリまで移動

$ cd ~/corundum/fpga/mqnic/AU200/fpga_100g/fpga

$ make

5. Corundumのツールのビルド

bitファイルをAlveoの不揮発性メモリに書き込んだり、Alveoをウォームブートするツールがcorundum/utilsに含まれており、そのビルドを以下のようにする。

$ cd ~/corundum/utils

$ make

6. Bitstream書き込み

Bitstreamの書き込みは2段階に分けて行う。まず、JTAG経由でBitstreamを揮発性メモリに書き込み、その後PCIe経由で不揮発性メモリに書き込む。

6.1 揮発性メモリへの書き込み

今回はVivadoのハードウェアマネージャを用いて書き込んだ。U200はマイクロUSBポートがあるため、ケーブルを繋げばJTAG経由で書き込むことができる。書き込み後はPCをウォームブートした。

6.2 不揮発性メモリへの書き込み

先程ビルドしたCorundumのツールに含まれているmqnic-fwを用いて書き込む。これはPCIe経由で書き込まれる。d(デバイス)オプションはmqnic-fwがオープンするデバイスのことで、PCIeのBDF値をlspciで確認し、指定した。

$ sudo ./mqnic-fw -d 01:00.0 -w ../fpga/mqnic/AU100/fpga_100g/fpga/fpga.bit

10分くらい待つと書き込み/検証が終了する。

次に、同じくmqnic-fwを用いて不揮発性メモリからブートする。

$ sudo ./mqnic-fw -d 01:00.0 -b

PCIe ID (device): 0000:01:00.0

PCIe ID (upstream port): 0000:00:01.0

FPGA ID: 0x04b37093

FPGA part: XCU200

FW ID: 0x00000000

FW version: 0.0.1.0

Board ID: 0x10ee90c8

Board version: 1.0.0.0

Build date: 2023-02-20 00:56:21 UTC (raw 0x63f2c535)

Git hash: c708bc45

Release info: 00000000

Flash type: SPI

Flash format: 0x01002012

Data width: 4

Manufacturer ID: 0x20

Memory type: 0xbb

Memory capacity: 0x21

Flash size: 128 MB

Write buffer size: 256 B

Erase block size: 4096 B

Flash segment 0: start 0x00000000 length 0x01002000

Flash segment 1: start 0x01002000 length 0x06ffe000

Default segment: 1

Fallback segment: 0

Selected: segment 1 start 0x01002000 length 0x06ffe000

Are you sure you want to boot from flash?

[y/N]: y

Preparing to reset device...

Disabling PCIe fatal error reporting on port...

Unbinding driver...

Triggering IPROG to reload FPGA...

Removing device...

Performing hot reset on upstream port...

Rescanning on upstream port...

Success, device is online!

最後にSuccess, device is online!と表示されればOK

7. デバイスドライバのロード

NICのドライバのプログラムがcorundum/modules/mqnicにあるのでビルドし、mqnic.koをロードする。

$ cd ~/corundum/modules/mqnic

$ make

$ sudo insmod mqnic.ko

dmesgを見ると以下のように出力された。

$ dmesg | grep mqnic

[86878.640479] mqnic 0000:01:00.0: mqnic PCI probe

[86878.640482] mqnic 0000:01:00.0: Vendor: 0x1234

[86878.640483] mqnic 0000:01:00.0: Device: 0x1001

[86878.640483] mqnic 0000:01:00.0: Subsystem vendor: 0x10ee

[86878.640484] mqnic 0000:01:00.0: Subsystem device: 0x90c8

[86878.640484] mqnic 0000:01:00.0: Class: 0x020000

[86878.640485] mqnic 0000:01:00.0: PCI ID: 0000:01:00.0

[86878.640488] mqnic 0000:01:00.0: Max payload size: 256 bytes

[86878.640489] mqnic 0000:01:00.0: Max read request size: 512 bytes

[86878.640490] mqnic 0000:01:00.0: Link capability: gen 3 x16

[86878.640490] mqnic 0000:01:00.0: Link status: gen 3 x16

[86878.640491] mqnic 0000:01:00.0: Relaxed ordering: enabled

[86878.640492] mqnic 0000:01:00.0: Phantom functions: disabled

[86878.640492] mqnic 0000:01:00.0: Extended tags: enabled

[86878.640492] mqnic 0000:01:00.0: No snoop: enabled

[86878.640493] mqnic 0000:01:00.0: NUMA node: -1

[86878.640494] mqnic 0000:01:00.0: PCI ID (bridge): 0000:00:01.0

[86878.640495] mqnic 0000:01:00.0: Link capability (bridge): gen 4 x16

[86878.640496] mqnic 0000:01:00.0: Link status (bridge): gen 3 x16

[86878.640500] mqnic 0000:01:00.0: 126.016 Gb/s available PCIe bandwidth (8.0 GT/s PCIe x16 link)

[86878.640502] mqnic 0000:01:00.0: can't disable ASPM; OS doesn't have ASPM control

[86878.640509] mqnic 0000:01:00.0: Control BAR size: 16777216

[86878.641258] mqnic 0000:01:00.0: Configured 64 IRQs

[86878.641287] mqnic 0000:01:00.0: Device-level register blocks:

[86878.641287] mqnic 0000:01:00.0: type 0xffffffff (v 0.0.1.0)

[86878.641288] mqnic 0000:01:00.0: type 0x0000c007 (v 0.0.1.0)

[86878.641289] mqnic 0000:01:00.0: type 0x0000c000 (v 0.0.1.0)

[86878.641289] mqnic 0000:01:00.0: type 0x00000000 (v 0.0.0.0)

[86878.641290] mqnic 0000:01:00.0: type 0x0000c006 (v 0.0.1.0)

[86878.641291] mqnic 0000:01:00.0: type 0x0000c080 (v 0.0.1.0)

[86878.641291] mqnic 0000:01:00.0: type 0x0000c008 (v 0.0.1.0)

[86878.641292] mqnic 0000:01:00.0: type 0x0000c110 (v 0.0.1.0)

[86878.641292] mqnic 0000:01:00.0: type 0x0000c101 (v 0.0.1.0)

[86878.641293] mqnic 0000:01:00.0: type 0x0000c120 (v 0.0.2.0)

[86878.641294] mqnic 0000:01:00.0: type 0x0000c140 (v 0.0.1.0)

[86878.641294] mqnic 0000:01:00.0: type 0x0000c150 (v 0.0.1.0)

[86878.641295] mqnic 0000:01:00.0: type 0x0000c150 (v 0.0.1.0)

[86878.641301] mqnic 0000:01:00.0: FPGA ID: 0x04b37093

[86878.641301] mqnic 0000:01:00.0: FW ID: 0x00000000

[86878.641302] mqnic 0000:01:00.0: FW version: 0.0.1.0

[86878.641302] mqnic 0000:01:00.0: Board ID: 0x10ee90c8

[86878.641303] mqnic 0000:01:00.0: Board version: 1.0.0.0

[86878.641303] mqnic 0000:01:00.0: Build date: 2023-02-20 00:56:21 UTC (raw: 0x63f2c535)

[86878.641305] mqnic 0000:01:00.0: Git hash: c708bc45

[86878.641305] mqnic 0000:01:00.0: Release info: 00000000

[86878.641313] mqnic 0000:01:00.0: IF offset: 0x00000000

[86878.641314] mqnic 0000:01:00.0: IF count: 2

[86878.641314] mqnic 0000:01:00.0: IF stride: 0x00800000

[86878.641315] mqnic 0000:01:00.0: IF CSR offset: 0x00040000

[86878.645080] i2c i2c-13: Added multiplexed i2c bus 14

[86878.645156] i2c i2c-13: Added multiplexed i2c bus 15

[86878.645230] i2c i2c-13: Added multiplexed i2c bus 16

[86878.645340] i2c i2c-13: Added multiplexed i2c bus 17

[86878.645343] pca954x 13-0074: registered 4 multiplexed busses for I2C switch pca9546

[86878.645396] at24 14-0050: supply vcc not found, using dummy regulator

[86878.672527] at24 14-0050: supply vcc not found, using dummy regulator

[86878.701854] at24 15-0050: supply vcc not found, using dummy regulator

[86878.703064] at24 15-0050: 256 byte 24c02 EEPROM, writable, 1 bytes/write

[86878.703165] at24 16-0054: supply vcc not found, using dummy regulator

[86878.704876] at24 16-0054: 1024 byte 24c08 EEPROM, writable, 1 bytes/write

[86878.704942] mqnic 0000:01:00.0: Read 2 MACs from Alveo BMC

[86878.705073] mqnic 0000:01:00.0: registered PHC (index 1)

[86878.705080] mqnic 0000:01:00.0: Creating interface 0

[86878.705193] mqnic 0000:01:00.0: Interface-level register blocks:

[86878.705196] mqnic 0000:01:00.0: type 0x0000c001 (v 0.0.4.0)

[86878.705201] mqnic 0000:01:00.0: type 0x0000c010 (v 0.0.1.0)

[86878.705204] mqnic 0000:01:00.0: type 0x0000c020 (v 0.0.1.0)

[86878.705207] mqnic 0000:01:00.0: type 0x0000c030 (v 0.0.1.0)

[86878.705210] mqnic 0000:01:00.0: type 0x0000c021 (v 0.0.1.0)

[86878.705213] mqnic 0000:01:00.0: type 0x0000c031 (v 0.0.1.0)

[86878.705216] mqnic 0000:01:00.0: type 0x0000c090 (v 0.0.1.0)

[86878.705218] mqnic 0000:01:00.0: type 0x0000c002 (v 0.0.2.0)

[86878.705222] mqnic 0000:01:00.0: type 0x0000c004 (v 0.0.3.0)

[86878.705233] mqnic 0000:01:00.0: IF features: 0x00000711

[86878.705238] mqnic 0000:01:00.0: Port count: 1

[86878.705241] mqnic 0000:01:00.0: Scheduler block count: 1

[86878.705243] mqnic 0000:01:00.0: Max TX MTU: 9214

[86878.705246] mqnic 0000:01:00.0: Max RX MTU: 9214

[86878.705250] mqnic 0000:01:00.0: Event queue offset: 0x00080000

[86878.705253] mqnic 0000:01:00.0: Event queue count: 64

[86878.705255] mqnic 0000:01:00.0: Event queue stride: 0x00000020

[86878.705260] mqnic 0000:01:00.0: TX queue offset: 0x00100000

[86878.705263] mqnic 0000:01:00.0: TX queue count: 8192

[86878.705265] mqnic 0000:01:00.0: TX queue stride: 0x00000020

[86878.705270] mqnic 0000:01:00.0: TX completion queue offset: 0x00200000

[86878.705272] mqnic 0000:01:00.0: TX completion queue count: 8192

[86878.705275] mqnic 0000:01:00.0: TX completion queue stride: 0x00000020

[86878.705279] mqnic 0000:01:00.0: RX queue offset: 0x00300000

[86878.705282] mqnic 0000:01:00.0: RX queue count: 256

[86878.705284] mqnic 0000:01:00.0: RX queue stride: 0x00000020

[86878.705288] mqnic 0000:01:00.0: RX completion queue offset: 0x00380000

[86878.705291] mqnic 0000:01:00.0: RX completion queue count: 256

[86878.705293] mqnic 0000:01:00.0: RX completion queue stride: 0x00000020

[86878.705298] mqnic 0000:01:00.0: Max desc block size: 8

[86878.711523] mqnic 0000:01:00.0: Port-level register blocks:

[86878.711527] mqnic 0000:01:00.0: type 0x0000c003 (v 0.0.2.0)

[86878.711530] mqnic 0000:01:00.0: Port features: 0x00000000

[86878.711533] mqnic 0000:01:00.0: Port TX status: 0x00000001

[86878.711536] mqnic 0000:01:00.0: Port RX status: 0x00000000

[86878.711542] mqnic 0000:01:00.0: Scheduler block-level register blocks:

[86878.711543] mqnic 0000:01:00.0: type 0x0000c040 (v 0.0.1.0)

[86878.711548] mqnic 0000:01:00.0: Scheduler type: 0x0000c040

[86878.711550] mqnic 0000:01:00.0: Scheduler offset: 0x00400000

[86878.711552] mqnic 0000:01:00.0: Scheduler channel count: 8192

[86878.711554] mqnic 0000:01:00.0: Scheduler channel stride: 0x00000004

[86878.711555] mqnic 0000:01:00.0: Scheduler count: 1

[86879.033033] mqnic 0000:01:00.0: Creating interface 1

[86879.033131] mqnic 0000:01:00.0: Interface-level register blocks:

[86879.033132] mqnic 0000:01:00.0: type 0x0000c001 (v 0.0.4.0)

[86879.033133] mqnic 0000:01:00.0: type 0x0000c010 (v 0.0.1.0)

[86879.033134] mqnic 0000:01:00.0: type 0x0000c020 (v 0.0.1.0)

[86879.033135] mqnic 0000:01:00.0: type 0x0000c030 (v 0.0.1.0)

[86879.033136] mqnic 0000:01:00.0: type 0x0000c021 (v 0.0.1.0)

[86879.033137] mqnic 0000:01:00.0: type 0x0000c031 (v 0.0.1.0)

[86879.033138] mqnic 0000:01:00.0: type 0x0000c090 (v 0.0.1.0)

[86879.033139] mqnic 0000:01:00.0: type 0x0000c002 (v 0.0.2.0)

[86879.033140] mqnic 0000:01:00.0: type 0x0000c004 (v 0.0.3.0)

[86879.033144] mqnic 0000:01:00.0: IF features: 0x00000711

[86879.033145] mqnic 0000:01:00.0: Port count: 1

[86879.033145] mqnic 0000:01:00.0: Scheduler block count: 1

[86879.033146] mqnic 0000:01:00.0: Max TX MTU: 9214

[86879.033146] mqnic 0000:01:00.0: Max RX MTU: 9214

[86879.033149] mqnic 0000:01:00.0: Event queue offset: 0x00080000

[86879.033150] mqnic 0000:01:00.0: Event queue count: 64

[86879.033151] mqnic 0000:01:00.0: Event queue stride: 0x00000020

[86879.033154] mqnic 0000:01:00.0: TX queue offset: 0x00100000

[86879.033154] mqnic 0000:01:00.0: TX queue count: 8192

[86879.033155] mqnic 0000:01:00.0: TX queue stride: 0x00000020

[86879.033158] mqnic 0000:01:00.0: TX completion queue offset: 0x00200000

[86879.033159] mqnic 0000:01:00.0: TX completion queue count: 8192

[86879.033159] mqnic 0000:01:00.0: TX completion queue stride: 0x00000020

[86879.033162] mqnic 0000:01:00.0: RX queue offset: 0x00300000

[86879.033163] mqnic 0000:01:00.0: RX queue count: 256

[86879.033163] mqnic 0000:01:00.0: RX queue stride: 0x00000020

[86879.033166] mqnic 0000:01:00.0: RX completion queue offset: 0x00380000

[86879.033167] mqnic 0000:01:00.0: RX completion queue count: 256

[86879.033167] mqnic 0000:01:00.0: RX completion queue stride: 0x00000020

[86879.033169] mqnic 0000:01:00.0: Max desc block size: 8

[86879.033243] mqnic 0000:01:00.0 enp1s0: renamed from eth0

[86879.036410] mqnic 0000:01:00.0: Port-level register blocks:

[86879.036411] mqnic 0000:01:00.0: type 0x0000c003 (v 0.0.2.0)

[86879.036414] mqnic 0000:01:00.0: Port features: 0x00000000

[86879.036415] mqnic 0000:01:00.0: Port TX status: 0x00000001

[86879.036417] mqnic 0000:01:00.0: Port RX status: 0x00000001

[86879.036420] mqnic 0000:01:00.0: Scheduler block-level register blocks:

[86879.036421] mqnic 0000:01:00.0: type 0x0000c040 (v 0.0.1.0)

[86879.036424] mqnic 0000:01:00.0: Scheduler type: 0x0000c040

[86879.036425] mqnic 0000:01:00.0: Scheduler offset: 0x00400000

[86879.036426] mqnic 0000:01:00.0: Scheduler channel count: 8192

[86879.036427] mqnic 0000:01:00.0: Scheduler channel stride: 0x00000004

[86879.036428] mqnic 0000:01:00.0: Scheduler count: 1

[86879.258770] mqnic 0000:01:00.0: mqnic_start_port on interface 0 netdev 0

[86879.653316] mqnic 0000:01:00.0: Registered device mqnic0

[86880.861057] mqnic 0000:01:00.0 enp1s0d1: renamed from eth0

[86880.893285] mqnic 0000:01:00.0: mqnic_start_port on interface 1 netdev 0

[86882.029959] IPv6: ADDRCONF(NETDEV_CHANGE): enp1s0d1: link becomes ready

8. ネットワークインターフェイスの設定

ドライバがロードされると新しいネットワークインターフェイスが生成される。自分の環境では、enp1s0d1という名前だった。

$ # リンクアップする

$ sudo ip link set dev enp1s0d1 up

$ # IPアドレスを付与する

$ sudo ip addr add 10.0.0.2/24 dev enp1s0d1

これでネットワークインターフェイスの状態を確認すると以下の様になった。

$ ip a

...(省略)...

4: enp1s0d1: <BROADCAST,MULTICAST,UP,LOWER_UP> mtu 1500 qdisc mq state UP group default qlen 1000

link/ether 00:0a:35:05:f5:8d brd ff:ff:ff:ff:ff:ff

inet 10.0.0.2/24 scope global enp1s0d1

valid_lft forever preferred_lft forever

U50のNIC化

U200のNIC化と同様の手順をU50でも行い、IPアドレスを10.0.0.3に割り当てた。また、U50にはマイクロUSBポートが無いため、揮発性メモリに書き込む際は、U50の付属品であるプログラミングケーブルを使用した。

iperf3でU200-U50間の通信テスト

それぞれNIC化したので通信してみる。また、U200とU50は、QSFP28のケーブルで接続した。

CorundumのドキュメントのGetting Startedにもあるようにiperf3を用いた。

U50が設置されたマシンがサーバ側(右)、U200が設置されたマシンがクライアント側(左)とし、通信できていることが確認できた。以下はその時のGIFアニメである。それぞれMTUは9000とした。

ブート時のドライバのロード

動作確認ができたので、ドライバ(mqnic.ko)をLinuxブート時にロードするようにした。

$ sudo cp mqnic.ko /lib/modules/$(uname -r)/kernel/drivers/

$ sudo depmod -a

$ sudo sh -c 'echo mqnic >> /etc/modules-load.d/modules.conf'

さらに、netplanでIPアドレスを固定しリブートしたところ、起動後は特に設定なく通信が行える状態になった。起動時のdmesgは以下の通りである。

$ dmesg | grep mqnic

[ 2.191625] mqnic: loading out-of-tree module taints kernel.

[ 2.191738] mqnic: module verification failed: signature and/or required key missing - tainting kernel

[ 2.192702] mqnic 0000:01:00.0: mqnic PCI probe

[ 2.192707] mqnic 0000:01:00.0: Vendor: 0x1234

[ 2.192710] mqnic 0000:01:00.0: Device: 0x1001

[ 2.192712] mqnic 0000:01:00.0: Subsystem vendor: 0x10ee

[ 2.192714] mqnic 0000:01:00.0: Subsystem device: 0x90c8

[ 2.192716] mqnic 0000:01:00.0: Class: 0x020000

[ 2.192718] mqnic 0000:01:00.0: PCI ID: 0000:01:00.0

[ 2.192727] mqnic 0000:01:00.0: Max payload size: 256 bytes

[ 2.192729] mqnic 0000:01:00.0: Max read request size: 512 bytes

[ 2.192732] mqnic 0000:01:00.0: Link capability: gen 3 x16

[ 2.192734] mqnic 0000:01:00.0: Link status: gen 3 x16

[ 2.192737] mqnic 0000:01:00.0: Relaxed ordering: enabled

[ 2.192739] mqnic 0000:01:00.0: Phantom functions: disabled

[ 2.192741] mqnic 0000:01:00.0: Extended tags: enabled

[ 2.192743] mqnic 0000:01:00.0: No snoop: enabled

[ 2.192745] mqnic 0000:01:00.0: NUMA node: -1

[ 2.192747] mqnic 0000:01:00.0: PCI ID (bridge): 0000:00:01.0

[ 2.192752] mqnic 0000:01:00.0: Link capability (bridge): gen 4 x16

[ 2.192755] mqnic 0000:01:00.0: Link status (bridge): gen 3 x16

[ 2.192763] mqnic 0000:01:00.0: 126.016 Gb/s available PCIe bandwidth (8.0 GT/s PCIe x16 link)

[ 2.192770] mqnic 0000:01:00.0: can't disable ASPM; OS doesn't have ASPM control

[ 2.192779] mqnic 0000:01:00.0: enabling device (0000 -> 0002)

[ 2.192791] mqnic 0000:01:00.0: Control BAR size: 16777216

[ 2.195330] mqnic 0000:01:00.0: Configured 64 IRQs

[ 2.195369] mqnic 0000:01:00.0: Device-level register blocks:

[ 2.195371] mqnic 0000:01:00.0: type 0xffffffff (v 0.0.1.0)

[ 2.195375] mqnic 0000:01:00.0: type 0x0000c007 (v 0.0.1.0)

[ 2.195379] mqnic 0000:01:00.0: type 0x0000c000 (v 0.0.1.0)

[ 2.195381] mqnic 0000:01:00.0: type 0x00000000 (v 0.0.0.0)

[ 2.195385] mqnic 0000:01:00.0: type 0x0000c006 (v 0.0.1.0)

[ 2.195387] mqnic 0000:01:00.0: type 0x0000c080 (v 0.0.1.0)

[ 2.195390] mqnic 0000:01:00.0: type 0x0000c008 (v 0.0.1.0)

[ 2.195393] mqnic 0000:01:00.0: type 0x0000c110 (v 0.0.1.0)

[ 2.195396] mqnic 0000:01:00.0: type 0x0000c101 (v 0.0.1.0)

[ 2.195398] mqnic 0000:01:00.0: type 0x0000c120 (v 0.0.2.0)

[ 2.195401] mqnic 0000:01:00.0: type 0x0000c140 (v 0.0.1.0)

[ 2.195404] mqnic 0000:01:00.0: type 0x0000c150 (v 0.0.1.0)

[ 2.195407] mqnic 0000:01:00.0: type 0x0000c150 (v 0.0.1.0)

[ 2.195416] mqnic 0000:01:00.0: FPGA ID: 0x04b37093

[ 2.195419] mqnic 0000:01:00.0: FW ID: 0x00000000

[ 2.195421] mqnic 0000:01:00.0: FW version: 0.0.1.0

[ 2.195424] mqnic 0000:01:00.0: Board ID: 0x10ee90c8

[ 2.195426] mqnic 0000:01:00.0: Board version: 1.0.0.0

[ 2.195428] mqnic 0000:01:00.0: Build date: 2023-02-20 00:56:21 UTC (raw: 0x63f2c535)

[ 2.195434] mqnic 0000:01:00.0: Git hash: c708bc45

[ 2.195436] mqnic 0000:01:00.0: Release info: 00000000

[ 2.195448] mqnic 0000:01:00.0: IF offset: 0x00000000

[ 2.195450] mqnic 0000:01:00.0: IF count: 2

[ 2.195452] mqnic 0000:01:00.0: IF stride: 0x00800000

[ 2.195455] mqnic 0000:01:00.0: IF CSR offset: 0x00040000

[ 2.316463] mqnic 0000:01:00.0: Resetting Alveo CMS

[ 2.522213] mqnic 0000:01:00.0: Read 2 MACs from Alveo BMC

[ 2.522363] mqnic 0000:01:00.0: registered PHC (index 1)

[ 2.522365] mqnic 0000:01:00.0: Creating interface 0

[ 2.522424] mqnic 0000:01:00.0: Interface-level register blocks:

[ 2.522425] mqnic 0000:01:00.0: type 0x0000c001 (v 0.0.4.0)

[ 2.522426] mqnic 0000:01:00.0: type 0x0000c010 (v 0.0.1.0)

[ 2.522427] mqnic 0000:01:00.0: type 0x0000c020 (v 0.0.1.0)

[ 2.522429] mqnic 0000:01:00.0: type 0x0000c030 (v 0.0.1.0)

[ 2.522430] mqnic 0000:01:00.0: type 0x0000c021 (v 0.0.1.0)

[ 2.522431] mqnic 0000:01:00.0: type 0x0000c031 (v 0.0.1.0)

[ 2.522432] mqnic 0000:01:00.0: type 0x0000c090 (v 0.0.1.0)

[ 2.522433] mqnic 0000:01:00.0: type 0x0000c002 (v 0.0.2.0)

[ 2.522434] mqnic 0000:01:00.0: type 0x0000c004 (v 0.0.3.0)

[ 2.522438] mqnic 0000:01:00.0: IF features: 0x00000711

[ 2.522439] mqnic 0000:01:00.0: Port count: 1

[ 2.522440] mqnic 0000:01:00.0: Scheduler block count: 1

[ 2.522441] mqnic 0000:01:00.0: Max TX MTU: 9214

[ 2.522442] mqnic 0000:01:00.0: Max RX MTU: 9214

[ 2.522445] mqnic 0000:01:00.0: Event queue offset: 0x00080000

[ 2.522446] mqnic 0000:01:00.0: Event queue count: 64

[ 2.522446] mqnic 0000:01:00.0: Event queue stride: 0x00000020

[ 2.522449] mqnic 0000:01:00.0: TX queue offset: 0x00100000

[ 2.522450] mqnic 0000:01:00.0: TX queue count: 8192

[ 2.522450] mqnic 0000:01:00.0: TX queue stride: 0x00000020

[ 2.522453] mqnic 0000:01:00.0: TX completion queue offset: 0x00200000

[ 2.522453] mqnic 0000:01:00.0: TX completion queue count: 8192

[ 2.522454] mqnic 0000:01:00.0: TX completion queue stride: 0x00000020

[ 2.522457] mqnic 0000:01:00.0: RX queue offset: 0x00300000

[ 2.522457] mqnic 0000:01:00.0: RX queue count: 256

[ 2.522458] mqnic 0000:01:00.0: RX queue stride: 0x00000020

[ 2.522460] mqnic 0000:01:00.0: RX completion queue offset: 0x00380000

[ 2.522461] mqnic 0000:01:00.0: RX completion queue count: 256

[ 2.522461] mqnic 0000:01:00.0: RX completion queue stride: 0x00000020

[ 2.522463] mqnic 0000:01:00.0: Max desc block size: 8

[ 2.525375] mqnic 0000:01:00.0: Port-level register blocks:

[ 2.525376] mqnic 0000:01:00.0: type 0x0000c003 (v 0.0.2.0)

[ 2.525378] mqnic 0000:01:00.0: Port features: 0x00000000

[ 2.525379] mqnic 0000:01:00.0: Port TX status: 0x00000001

[ 2.525380] mqnic 0000:01:00.0: Port RX status: 0x00000000

[ 2.525384] mqnic 0000:01:00.0: Scheduler block-level register blocks:

[ 2.525384] mqnic 0000:01:00.0: type 0x0000c040 (v 0.0.1.0)

[ 2.525387] mqnic 0000:01:00.0: Scheduler type: 0x0000c040

[ 2.525387] mqnic 0000:01:00.0: Scheduler offset: 0x00400000

[ 2.525388] mqnic 0000:01:00.0: Scheduler channel count: 8192

[ 2.525388] mqnic 0000:01:00.0: Scheduler channel stride: 0x00000004

[ 2.525389] mqnic 0000:01:00.0: Scheduler count: 1

[ 2.850209] mqnic 0000:01:00.0: Creating interface 1

[ 2.850277] mqnic 0000:01:00.0: Interface-level register blocks:

[ 2.850278] mqnic 0000:01:00.0: type 0x0000c001 (v 0.0.4.0)

[ 2.850279] mqnic 0000:01:00.0: type 0x0000c010 (v 0.0.1.0)

[ 2.850280] mqnic 0000:01:00.0: type 0x0000c020 (v 0.0.1.0)

[ 2.850280] mqnic 0000:01:00.0: type 0x0000c030 (v 0.0.1.0)

[ 2.850281] mqnic 0000:01:00.0: type 0x0000c021 (v 0.0.1.0)

[ 2.850282] mqnic 0000:01:00.0: type 0x0000c031 (v 0.0.1.0)

[ 2.850282] mqnic 0000:01:00.0: type 0x0000c090 (v 0.0.1.0)

[ 2.850283] mqnic 0000:01:00.0: type 0x0000c002 (v 0.0.2.0)

[ 2.850283] mqnic 0000:01:00.0: type 0x0000c004 (v 0.0.3.0)

[ 2.850287] mqnic 0000:01:00.0: IF features: 0x00000711

[ 2.850288] mqnic 0000:01:00.0: Port count: 1

[ 2.850288] mqnic 0000:01:00.0: Scheduler block count: 1

[ 2.850289] mqnic 0000:01:00.0: Max TX MTU: 9214

[ 2.850289] mqnic 0000:01:00.0: Max RX MTU: 9214

[ 2.850291] mqnic 0000:01:00.0: Event queue offset: 0x00080000

[ 2.850292] mqnic 0000:01:00.0: Event queue count: 64

[ 2.850292] mqnic 0000:01:00.0: Event queue stride: 0x00000020

[ 2.850295] mqnic 0000:01:00.0: TX queue offset: 0x00100000

[ 2.850295] mqnic 0000:01:00.0: TX queue count: 8192

[ 2.850296] mqnic 0000:01:00.0: TX queue stride: 0x00000020

[ 2.850298] mqnic 0000:01:00.0: TX completion queue offset: 0x00200000

[ 2.850299] mqnic 0000:01:00.0: TX completion queue count: 8192

[ 2.850299] mqnic 0000:01:00.0: TX completion queue stride: 0x00000020

[ 2.850302] mqnic 0000:01:00.0: RX queue offset: 0x00300000

[ 2.850302] mqnic 0000:01:00.0: RX queue count: 256

[ 2.850303] mqnic 0000:01:00.0: RX queue stride: 0x00000020

[ 2.850305] mqnic 0000:01:00.0: RX completion queue offset: 0x00380000

[ 2.850305] mqnic 0000:01:00.0: RX completion queue count: 256

[ 2.850306] mqnic 0000:01:00.0: RX completion queue stride: 0x00000020

[ 2.850307] mqnic 0000:01:00.0: Max desc block size: 8

[ 2.852986] mqnic 0000:01:00.0: Port-level register blocks:

[ 2.852987] mqnic 0000:01:00.0: type 0x0000c003 (v 0.0.2.0)

[ 2.852988] mqnic 0000:01:00.0: Port features: 0x00000000

[ 2.852990] mqnic 0000:01:00.0: Port TX status: 0x00000001

[ 2.852991] mqnic 0000:01:00.0: Port RX status: 0x00000001

[ 2.852995] mqnic 0000:01:00.0: Scheduler block-level register blocks:

[ 2.852995] mqnic 0000:01:00.0: type 0x0000c040 (v 0.0.1.0)

[ 2.852998] mqnic 0000:01:00.0: Scheduler type: 0x0000c040

[ 2.852998] mqnic 0000:01:00.0: Scheduler offset: 0x00400000

[ 2.852999] mqnic 0000:01:00.0: Scheduler channel count: 8192

[ 2.852999] mqnic 0000:01:00.0: Scheduler channel stride: 0x00000004

[ 2.853000] mqnic 0000:01:00.0: Scheduler count: 1

[ 3.188797] mqnic 0000:01:00.0: Registered device mqnic0

[ 3.205073] mqnic 0000:01:00.0 enp1s0: renamed from eth0

[ 6.415371] mqnic 0000:01:00.0: New MTU: 9000

[ 6.418503] mqnic 0000:01:00.0: mqnic_start_port on interface 1 netdev 0